Community Newsletter: November 2013

- Message from the Chair

Shishpal Rawat talks about the latest in standards innovation - New UPF Tutorial on Low Power Design

Complete set of technical tutorials from DVCon available

- In the News

IP-XACT extensions, OCP-IP

- Events

SystemC Japan Trip Report by Dennis Brophy

Stan Krolikoski reveals what’s on the horizon for DVCon 2014

2013 Taiwan Accellera User’s Forum

- Setting the Standard Blog

Yatin Trivedi talks Community, Collaboration and Standards

Message from the Chair

Season's Greetings from Accellera Systems Initiative! Exciting things are happening in the world of intellectual property (IP) standards. We recently acquired the OCP 3.0 standard and supporting infrastructure, which facilitates reuse of IP blocks used in the design of semiconductor products. And earlier this year, we announced enhancement of the IP-XACT standard with new vendor extension for analog/mixed-signal and low-power designs. These standards complement other IP interoperability standards developed by Accellera, including SystemC and transaction-level modeling.

Season's Greetings from Accellera Systems Initiative! Exciting things are happening in the world of intellectual property (IP) standards. We recently acquired the OCP 3.0 standard and supporting infrastructure, which facilitates reuse of IP blocks used in the design of semiconductor products. And earlier this year, we announced enhancement of the IP-XACT standard with new vendor extension for analog/mixed-signal and low-power designs. These standards complement other IP interoperability standards developed by Accellera, including SystemC and transaction-level modeling.

What does this mean for the industry?

Accellera has been collaborating on IP-standards for many years and sees the industry opportunity to consolidate standardization practices through established technologies such as SystemC TLM, IP-XACT and OCP-IP. Under one roof, the combined technologies better serve the industry to provide a one-stop, front-end electronic design resource to address interoperability of IP design that will improve reuse, ultimately increasing designer productivity and reducing development costs.

With Accellera’s broad exposure to the electronic design industry, standards can be made more readily available and adopted. Through our partnership with the IEEE-SA, we make standards freely available to the worldwide engineering community. This not only provides a huge benefit to the industry as a whole, but to the individual engineer responsible for making a faster, cheaper, better product in less time.

Read more about our partnership with the IEEE-SA in our blog.

As we forge ahead into 2014 and the next era of electronics, IP standards are crucial to the successful design process. Accellera is thrilled to lead the way.

From all of us at Accellera, we wish you a safe, happy and healthy holiday season!

Sincerely,

Shishpal Rawat, Accellera Systems Initiative Chair

November 2013

New UPF Tutorial on Low Power Design

The "Low Power Design, Verification, and Implementation with IEEE 1801™ UPF™" tutorial covers the basics of Accellera UPF and then focuses on the features of IEEE 1801 that enable the description of more sophisticated power management systems. The tutorial also provides recommendations regarding migration from Accellera UPF to IEEE 1801 and the methodology changes that are required. And, it presents a UPF-based design flow highlighting the practical aspects of using UPF for verification and implementation. This flow is illustrated with practical examples representative of real systems and includes best practices for successful design and verification of low power systems with UPF. Watch now!

The "Low Power Design, Verification, and Implementation with IEEE 1801™ UPF™" tutorial covers the basics of Accellera UPF and then focuses on the features of IEEE 1801 that enable the description of more sophisticated power management systems. The tutorial also provides recommendations regarding migration from Accellera UPF to IEEE 1801 and the methodology changes that are required. And, it presents a UPF-based design flow highlighting the practical aspects of using UPF for verification and implementation. This flow is illustrated with practical examples representative of real systems and includes best practices for successful design and verification of low power systems with UPF. Watch now!

Additional technical tutorials presented at DVCon 2013 are also available:

- User Experiences at the Forefront of Mixed-Signal Design and Verification

- Increasing Productivity with SystemC in Complex System Design and Verification

- Lessons from the Trenches: Migrating Legacy Verification Environments to UVM

In the News

Accellera Acquires OCP 3.0 Standard and Supporting Infrastructure

![]() The OCP-IP 3.0 standard complements other IP interoperability standards developed by Accellera such as SystemC for transaction-level modeling and IP-XACT. The combination of these standards under one organization will result in more efficient ways to address the need for interoperability of IP design and will improve reuse.

The OCP-IP 3.0 standard complements other IP interoperability standards developed by Accellera such as SystemC for transaction-level modeling and IP-XACT. The combination of these standards under one organization will result in more efficient ways to address the need for interoperability of IP design and will improve reuse.

Read the press release >

Visit the OCP community >

Download the OCP 3.0 specification >

New IP-XACT Vendor Extensions for Analog/Mixed-Signal and Low-Power Designs

IP-XACT is an industry-wide standard that provides a formal way to model IP and enable reuse of IP for future designs. The Accellera vendor extensions are recommended practices that do not change the IEEE 1685 standard, but enhance the functionality and flexibility of that standard to address multiple users of multiple tools in emerging areas of design such as analog/mixed-signal, physical design planning and power.

IP-XACT is an industry-wide standard that provides a formal way to model IP and enable reuse of IP for future designs. The Accellera vendor extensions are recommended practices that do not change the IEEE 1685 standard, but enhance the functionality and flexibility of that standard to address multiple users of multiple tools in emerging areas of design such as analog/mixed-signal, physical design planning and power.

Read the press release >

Download the extensions

Events

SystemC Japan Trip Report

by Dennis Brophy, Accellera Vice-Chair

This past June, the annual SystemC Japan seminar was held in Yokohama, Japan. More than 250 SystemC users and tools suppliers met to exchange information and ideas on how to best apply SystemC to the pressing system design and verification challenges we all face.

This past June, the annual SystemC Japan seminar was held in Yokohama, Japan. More than 250 SystemC users and tools suppliers met to exchange information and ideas on how to best apply SystemC to the pressing system design and verification challenges we all face.

Accellera is one of the event sponsors. Stan Krolikoski, Accellera Secretary, and I opened the conference with a presentation where I updated the attendees on Accellera’s standardization activities and Stan updated them on our collaboration with the IEEE. As Stan is also the chair of the IEEE Design Automation Standards Committee, having him address the Accellera/IEEE collaboration allowed us to share information from the expert.

The SystemC Japan seminar is held in Japanese, and Accellera is indebted to be allowed to share the introduction portion with the attendees in English. The rest of the program offered presentations by Japanese users of SystemC ranging from leveraging IP-XACT with SystemC, efficient DSP design using high-level design technology, efficient verification in large-scale systems to integration of FPGA prototypes and virtual prototypes. The day-long seminar was followed by a social event that allowed attendees to mingle, talk and visit sponsor exhibit tables.

What impressed me were the wide variety of topics covered in the seminar ranging from silicon to software and electronic systems in silicon to systems in automobiles. SystemC has broad appeal and a diverse set of application areas. The SystemC Japan group is active year round, and they share updates on current activities and plans at www.systemcjapan.com. Check them out! They are planning the 2014 event now.

On the Road to DVCon 2014

by Stan Krolikoski, DVCon 2014 Chair and Accellera Secretary

After yet another record year for attendance in 2013, DVCon (Design and Verification Conference) returns for 2014 determined to raise the bar even higher. New DVCon 2014 features that have been added to appeal to even more attendees are:

After yet another record year for attendance in 2013, DVCon (Design and Verification Conference) returns for 2014 determined to raise the bar even higher. New DVCon 2014 features that have been added to appeal to even more attendees are:

- An expanded focus on design, especially higher level, low power and analog/mixed-signal design

- An expanded day of sponsored tutorials on DVCon Thursday

- Vendor exhibition on Monday in addition to the traditional Tuesday and Wednesday exhibition hours

- Coverage of the latest Accellera standards, including a tutorial focused on the latest member of the family, OCP

Add to all of this DVCon’s extensive coverage of the latest functional verification happenings, and DVCon 2014 promises to be a "can’t miss" event for design and verification engineers worldwide.

Upcoming Event: 2013 Taiwan Accellera User’s Forum

December 19, 2013 — Hsinchu, Taiwan

December 20, 2013 — Tainan, Taiwan

Community, Collaboration and Standards

Setting the Standard Blog

by Yatin Trivedi, Member of the Board of Directors, Accellera

EDA tools/methodologies and semiconductor IP creation are strongly driven by standards. Dating back to the 1980s, standards have helped shape electronic design industry — from the way we design silicon to the way we do business. Indeed, Accellera was formed from a merger of two leading standards bodies in the early 1990s, VHDL International (VI) and Open Verilog International (OVI), to promote cooperation among users and vendors as well as address tool interoperability and design flows. And as the saying goes, since that time, we’ve come a long way baby!

Since its inception, Accellera has delivered over 19 standards and implementations of which nine are now IEEE standards and governed by the IEEE-Standards Association (IEEE-SA), the leading consensus-building organization that nurtures, develops and advances global technologies. Their work drives the functionality, capabilities and interoperability of a wide range of products and services that transform the way people live, work and communicate.

Accellera has now worked closely with the IEEE-SA for more than 25 years — since the early days of VHDL (IEEE Std. 1076-1987) and Verilog HDL (IEEE Std. 1364-1995) — to provide the seed work for many of today’s ubiquitous electronic design automation standards. Through an ongoing partnership with the IEEE-SA, standards developed by Accellera are contributed to the IEEE’s standards development process for formal standardization and governance. Accellera further leverages the IEEE’s relationship with the IEC under a dual-logo program to bring these standards to the international community.

Developing standards is only a part of the activities at Accellera. No standard is really useful unless it is put into practice and widely adopted by the community for which it is intended. Accellera especially invests its volunteer efforts to increase the adoption of standards by the semiconductor industry practitioners, i.e., the users, academia and vendors. For example, its flagship DVCon Conference and Exhibition provides an excellent annual venue for designers and verification engineers to learn standards-based methodology and interoperability using EDA tools and semiconductor IP.

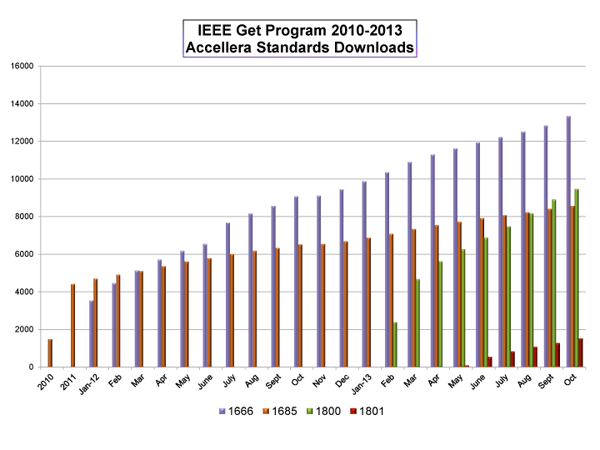

Starting in 2006, Accellera went one step further in its collaboration with the IEEE-SA. In order to ensure free access to the most widely used EDA and semiconductor IP standards, Accellera became a sponsor in the IEEE Get program which grants public access to view and download select IEEE standards at no charge. Standards currently available through the IEEE Get program include:

- IEEE 1685™ Standard: IP-XACT, Standard Structure for Packaging, Integrating, and Reusing IP within Tool Flows

- IEEE 1666™ Standard: SystemC™ Language Reference Manual

- IEEE 1800™ Standard: SystemVerilog Unified Hardware Design, Specification, and Verification Language Reference Manual

- IEEE 1801™ Standard: Design and Verification of Low Power Integrated Circuits (also known as Unified Power Format)

You can find all of the available standards and download them at no cost by visiting the Accellera Downloads page or IEEE Get webpage. Accellera plans to continue sponsoring additional standards as the work of current IEEE working groups (WGs) is ratified through the IEEE-SA standardization process.

The IEEE Get program has yielded some exceptionally good results in the past four years. The chart below shows the number of downloads of Accellera-sponsored standards available through the IEEE Get program. In order to show the most recent download activity, the first two years (2010 and 2011) are aggregated for the entire year, whereas 2012 and 2013 (year-to-date) are shown for each month. After launching the program with IP-XACT (originally under The SPIRIT Consortium before its merger with Accellera), SystemC, SystemVerilog and UPF standards were gradually added to the IEEE Get program. For SystemC, the download data only includes the most recent release of the standard (IEEE 1666-2012). For trivia buffs, it would be interesting to note that you can download the most widely used communication standards (IEEE 802 family) from the IEEE Get webpage. You know you are in good company!

Establishing a standard across the industry can determine success or failure for a product or even a company. Making a standard freely available helps accelerate adoption and improves the overall lifecycle of the standard — from the users who develop the leading edge technologies to the vendors that provide the tools and services that bring those technologies to life. Not to forget the free access to standards that also encourages students and researchers in academia to develop skills that eventually help the industry.

IEEE Get is a very effective program leveraged by Accellera to serve our community. We welcome you to join us and participate in standards development. Help us build a strong collaborative and inclusive community around standards. Of course, if you are already a member of Accellera, we thank you. Your membership dues and volunteer participation are serving the entire industry. Kudos!

This blog post is also available on www.semiengineering.com.

2013 Global Sponsors

|

|

|

|

Event Sponsorship

Are you interested in becoming a Global Sponsor for 2014 or sponsoring a specific Accellera event? Find out more about our Sponsorship Packages.

EDITORIAL CONTACT

If you have questions or need assistance, please contact:

Jill Jacobs

This email address is being protected from spambots. You need JavaScript enabled to view it.

Add accellera.org to your list of acceptable domains to make sure you receive updates from Accellera Systems Initiative.

Copyright 2013 Accellera Systems Initiative