#### Universal Verification Methodology (UVM)

#### Verifying Blocks to IP to SOCs and Systems

Organizers: Dennis Brophy Stan Krolikoski Yatin Trivedi

San Diego, CA June 5, 2011

## **Workshop Outline**

| 10:00am – 10:05am | Dennis Brophy    | Welcome                          |

|-------------------|------------------|----------------------------------|

| 10:05am – 10:45am | Sharon Rosenberg | UVM Concepts and Architecture    |

| 10:45am – 11:25am | Tom Fitzpatrick  | UVM Sequences and Phasing        |

| 11:25am – 11:40am | Break            |                                  |

| 11:40am – 12:20pm | Janick Bergeron  | UVM TLM2 and Register Package    |

| 12:20pm – 12:50pm | Ambar Sarkar     | Putting Together UVM Testbenches |

| 12:50pm – 1:00pm  | All              | Q & A                            |

# **Workshop Outline**

| ✓10:00am – 10:05am | Dennis Brophy    | Welcome                          |

|--------------------|------------------|----------------------------------|

| 10:05am – 10:45am  | Sharon Rosenberg | UVM Concepts and Architecture    |

| 10:45am – 11:25am  | Tom Fitzpatrick  | UVM Sequences and Phasing        |

| 11:25am – 11:40am  | Break            |                                  |

| 11:40am – 12:20pm  | Janick Bergeron  | UVM TLM2 and Register Package    |

| 12:20pm – 12:50pm  | Ambar Sarkar     | Putting Together UVM Testbenches |

| 12:50pm – 1:00pm   | All              | Q & A                            |

#### **UVM Concepts and Architecture**

#### Sharon Rosenberg Cadence Design Systems

# **UVM Core Capabilities**

- Universal Verification Methodology

- A methodology and a class library for building advanced reusable verification components

- Methodology first!

- Relies on strong, proven industry foundations

- The core of the success is adherence to a standard (architecture, stimulus creation, automation, factory usage, etc')

- We added useful enablers and tuned a few to make UVM1.0 more capable

- This section covers the high-level concepts of UVM

- Critical to successful deployment of UVM

- Mature and proven

## **The Goal: Automation**

UTOMATION

Coverage Driven Verification (CDV) environments Coverage Automated Stimulus Generation Independent Checking **Scoreboard** Coverage Collection Checking Coverage Coverage seed **Monitor Monitor** 23098432 38748932 23432239 17821961 10932893 20395483 18902904 23843298 23432432 24324322 Random DUT 55252255 **Driver** 09273822 Sequence **APB** UART 13814791 Tests 4098e092 Generator 23432424 24242355 **Packaged for Reuse** 25262622 26452454 4524522 acceller

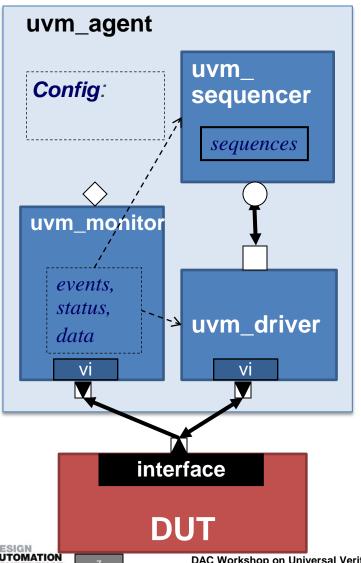

#### **UVM Architecture:** Interface Level Encapsulation

- Agents provide all the verification logic for a device in the system

- Instantiation and connection logic is done by the developer in a standard manner

- A Standard agent has:

- Sequencer for generating traffic

- Driver to drive the DUT

- Monitor

- The monitor is independent of the driving logic

- Agent has standard configuration parameters for the integrator to use

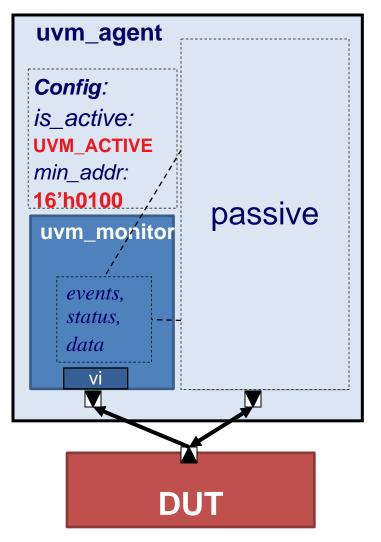

# **Agent Standard Configuration**

• A standard agent is configured using an enumeration field: **is\_active**

- UVM\_ACTIVE:

- Actively drive an interface or device

- Driver, Sequencer and Monitor are allocated

- UVM\_PASSIVE:

- Only the Monitor is allocated

- Still able to do checking and collect coverage

- Other user-defined configuration parameters can also be added

- Example: address configuration for slave devices

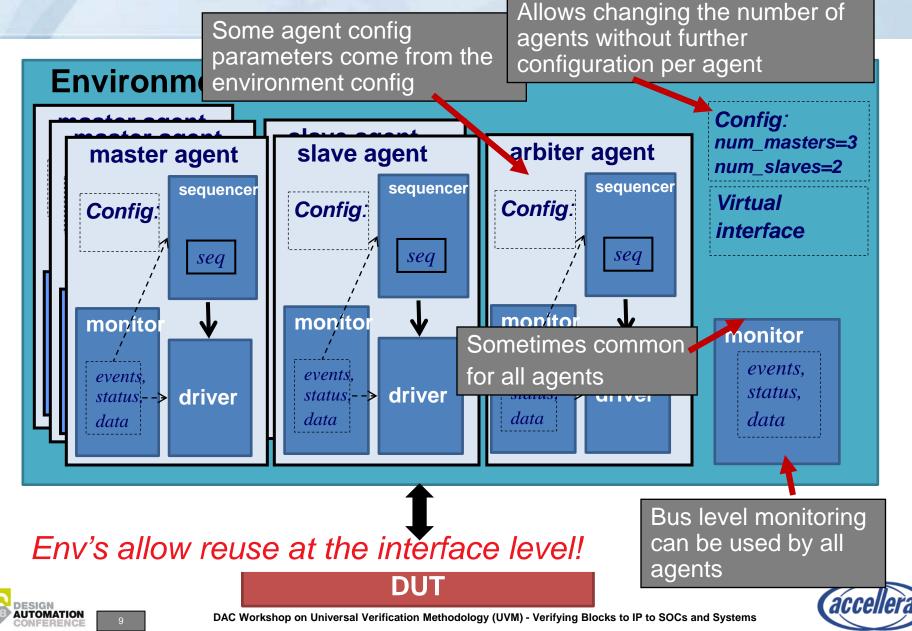

#### uvm: Configurable Bus Environment

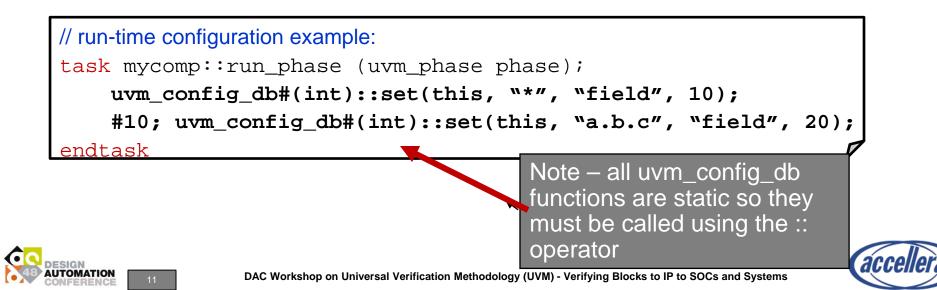

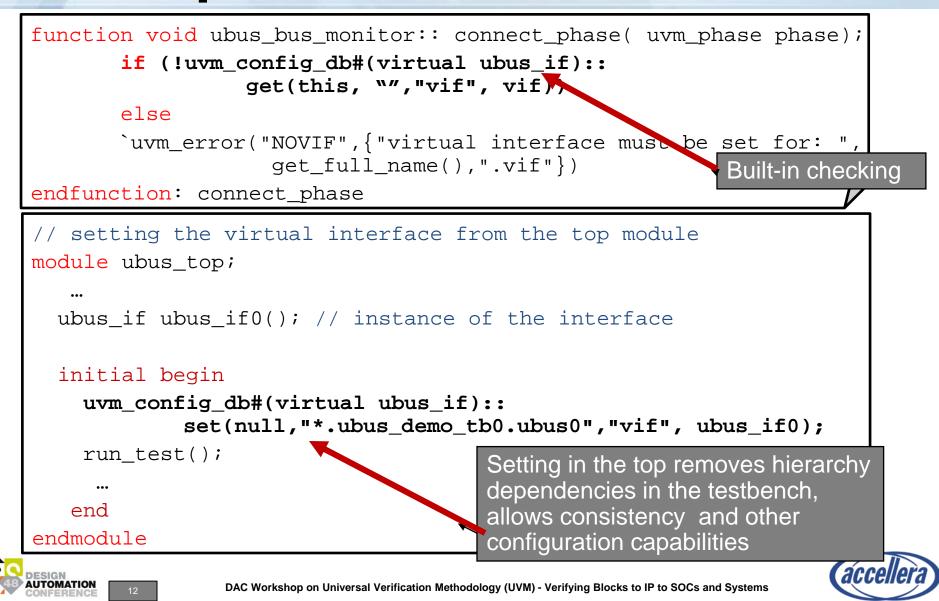

### **UVM Configuration Mechanism**

- The configuration mechanism allows a powerful way for attribute configuration

- Configuration mechanism advantages:

- Mechanism semantic allows an upper component to override contained components values

- No file changes are required

- Can configure attributes at various hierarchy locations

- Wild cards and regular expressions allow configuration of multiple attributes with a single command

- Debug capabilities

- Support for user defined types (e.g. SV virtual interfaces)

- Run-time configuration support

- Type safe solution

#### UVM1.0 Configuration Enhancements (Cont')

Check if configuration exists

class uvm\_config\_db#(type T=int) extends uvm\_resource\_db#(T);

static function bit set ( uvm\_component cntxt,

string inst\_name,string field\_name, T value);

static function bit get ( uvm\_component cntxt,

string inst\_name,string field\_name, ref T value);

static function bit exists(...);

static function void dump();

static task wait\_modified(...);

endclass

Wait for value to be set in

the uvm\_config\_db

#### Virtual Interface Configuration Example

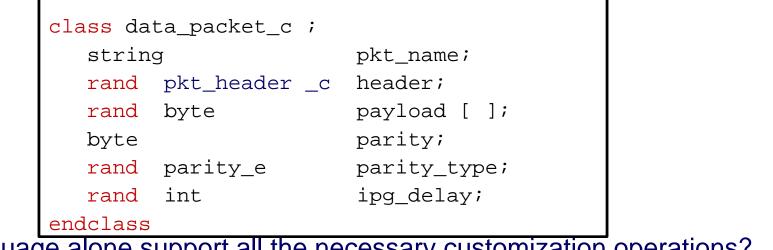

#### Where SV Language Stops and UVM Begins Example: Data Items

Does language alone support all the necessary customization operations?

Randomization

Printing

Cloning

Comparing

Copying

Packing

Transaction Recording

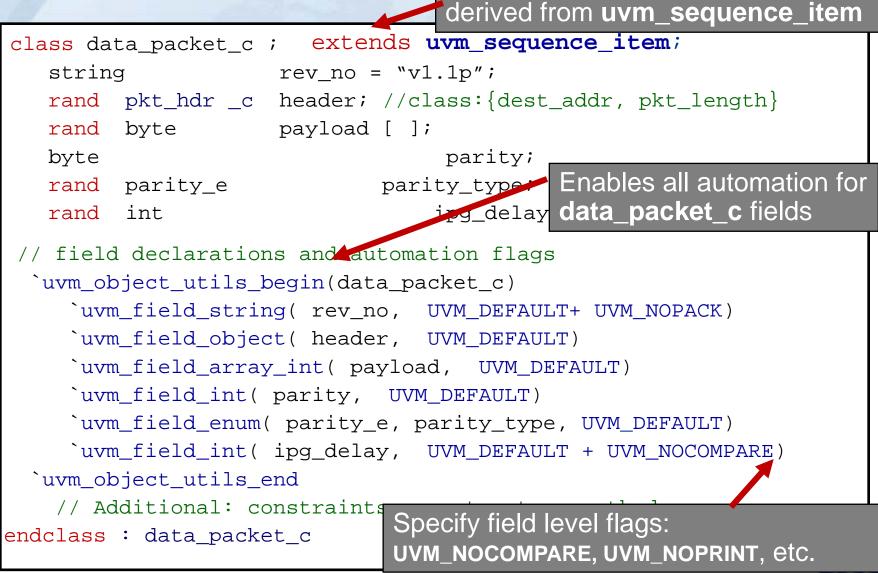

#### **Enabling Data Item Automation**

DAC Workshop on Universal Verification Methodology (UVM) - Verifying Blocks to IP to SOCs and Systems

acceller

#### Data Type Automation

|                                                                                                                                                                                                                                                                                                                        | Na       | me                                                            | Туре                                                                                           | Valu   | е           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------|-------------|

| <pre>// two instances of data_packet_c data_packet_c packet1, packet2; initial begin     // create and randomize new pack     packet1 = new("my_packet");     assert(packet1.randomize()); // print using UVM automation     packet1.print();     // copy using UVM automation     packet2 = new("copy_packet");</pre> |          | copy_packe<br>rev_no:<br>header:<br>dest_a                    | <pre>data_packet_c string pkt_header_c integral integral da(integral) t: (data_packet_c@</pre> |        | р<br>0<br>5 |

| <pre>packet2.copy(packet1));<br/>packet2.rev_no = "v1.1s";<br/>// print using UVM tree printer<br/>packet2.print(<br/>uvm_default_tree_printer);<br/>end<br/>UVM also allows manual<br/>implementation for performance or<br/>other reasons</pre>                                                                      | pa<br>ip | <pre>payload:    [0]: '    [1]: '    [28]:    } parity:</pre> | h2a<br>hdb<br><br>'h21<br>'hd9<br>ype: GOOD_PARITY                                             | accent | Pra         |

DAC Workshop on Universal Verification Methodology (UVM) - Verifying Blocks to IP to SOCs and Systems

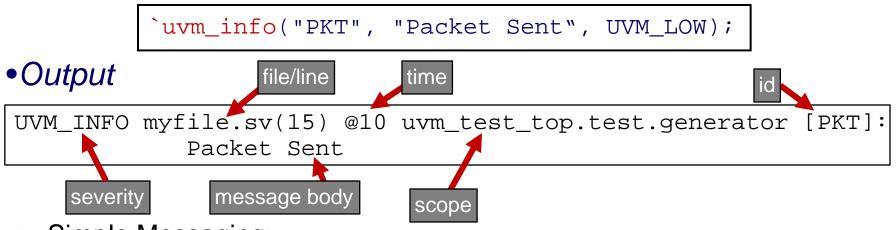

# **UVM Messaging Facility**

- Messages print trace information with advantages over \$display:

- Aware of its hierarchy/scope in testbench

- Allows filtering based on hierarchy, verbosity, and time

- Simple Messaging:

- `uvm\_\*(string id, string message, <verbosity>);

- Where \* (severity) is one of fatal, error, warning, info

- <verbosity> is only valid for uvm\_info

### **UVM Sequences**

- A sequencer controls the generation of random stimulus by executing sequences

- A sequence captures meaningful streams of transactions

- A simple sequence is a random transaction generator

- A more complex sequence can contain timing, additional constraints, parameters

#### <u>Sequences:</u>

- Allow reactive generation react to DUT

- Have many built-in capabilities like interrupt support, arbitration schemes, automatic factory support, etc

- Can be nested inside other sequences

- Are reusable at higher levels

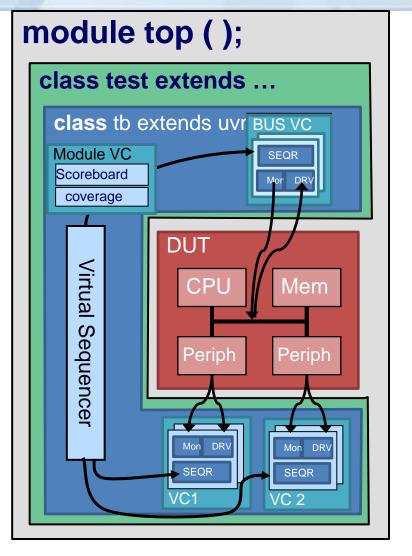

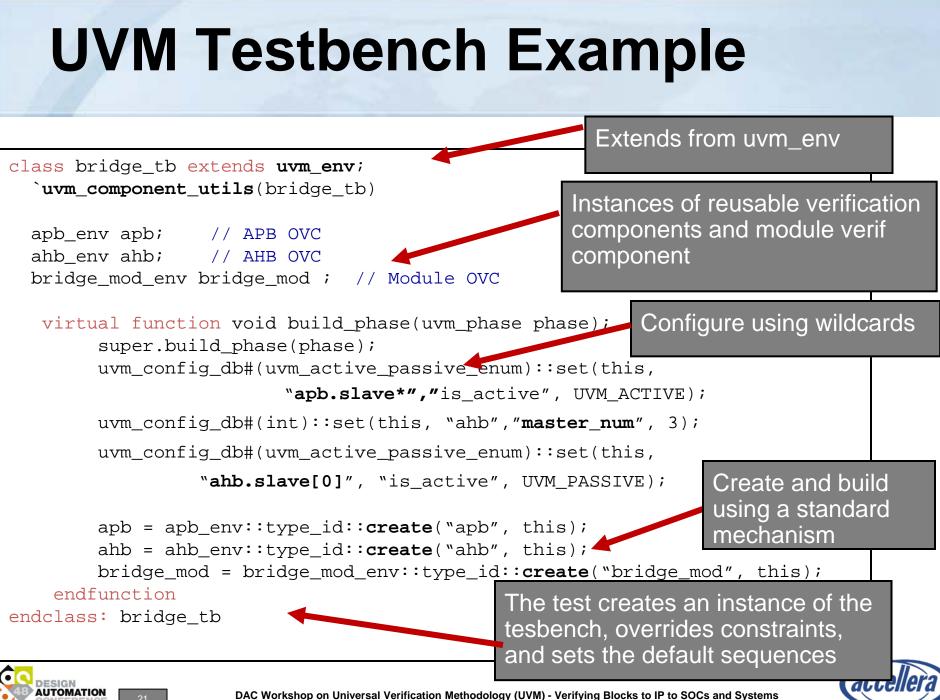

# **UVM Tests and Testbenches**

- Placing all components in the test requires lot of duplication

- Separate the env configuration and the test

- TB class instantiates and configures reusable components

- Tests instantiate a testbench

- Specify the nature of generated traffic

- Can modify configuration parameters as needed

- Benefits

- Tests are shorter, and descriptive

- Less knowledge to create a test

- Easier to maintain changes are done in a central location

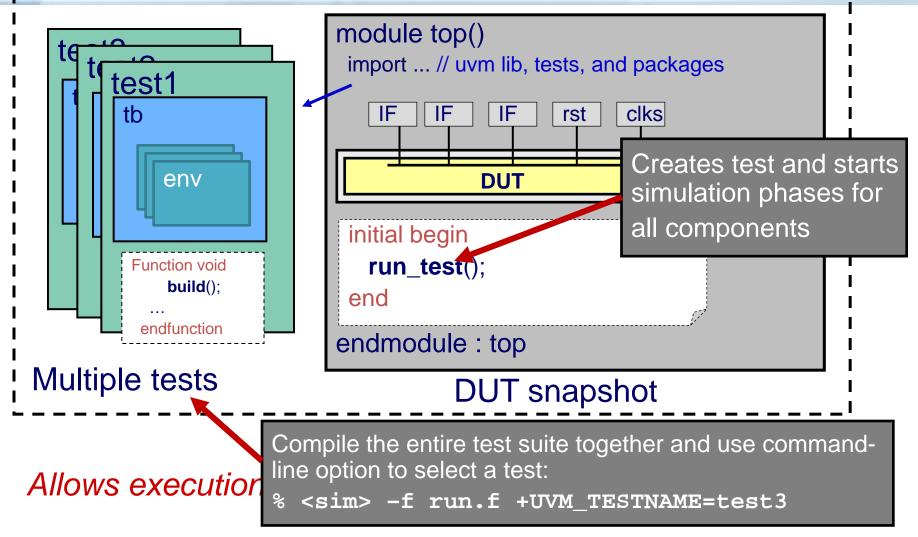

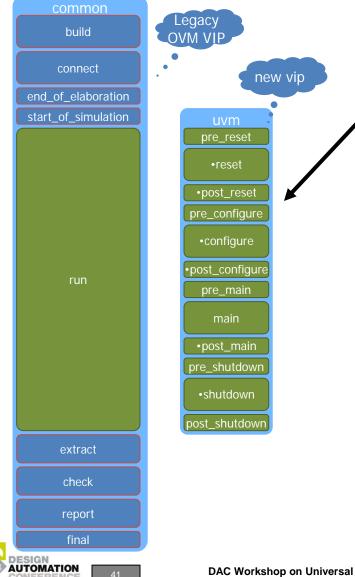

# **UVM Simulation Phases**

- When using classes, you need to manage environment creation at run-time

- Test execution is divided to phases

- Configuration, testbench creation, run-time, check, etc

- Unique tasks are performed in each simulation phase

- Set-up activities are performed during "testbench creation" while expected results may be addressed in "check"

- Phases run in order next phase does not begin until previous phase is complete

- UVM provides set of standard phases enabling VIP plug&play

- Allows orchestrating the activity of components that were created by different resources

### **UVM Simulation Phases**

UVM component's built-in phases - run in order

Note: All phases except run() execute in zero time

| build                                  | Build Top-Level Testbench Topology              |  |

|----------------------------------------|-------------------------------------------------|--|

| connect                                | Connect environment topology                    |  |

| end of elaboration                     | Post-elaboration activity (e.g. print topology) |  |

| start_of_simulation                    | Configure verification components               |  |

| reset<br>configure<br>main<br>shutdown | tasks - Run-time execution of the test          |  |

| extract                                | Gathers details on the final DUT state          |  |

| check                                  | Processes and checks the simulation results.    |  |

| report 🔨                               | Simulation results analysis and reporting       |  |

All phase names have postfix "\_phase"

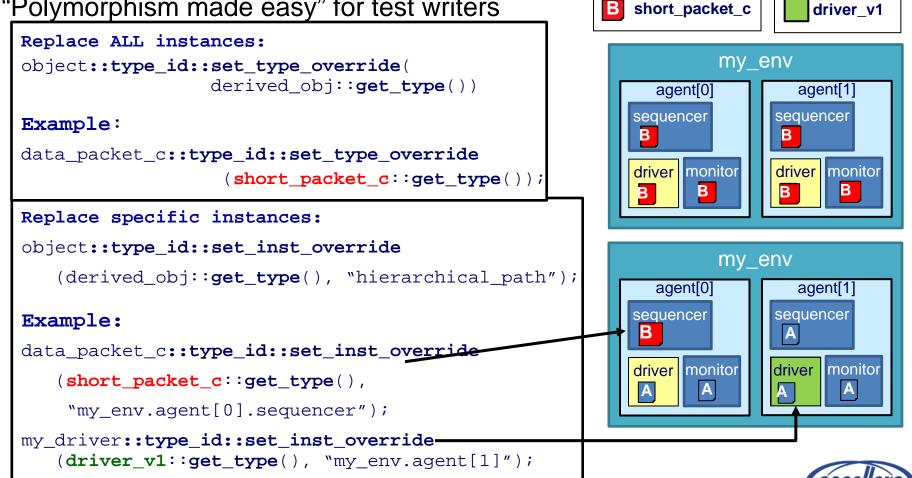

#### **Overriding SV Components** and Data Objects

- UVM Provides a mechanism for overriding the default data items and objects in a testbench

- "Polymorphism made easy" for test writers

data\_packet\_c

Α

driver

DAC Workshop on Universal Verification Methodology (UVM) - Verifying Blocks to IP to SOCs and Systems

#### The Test Launching Mechanism

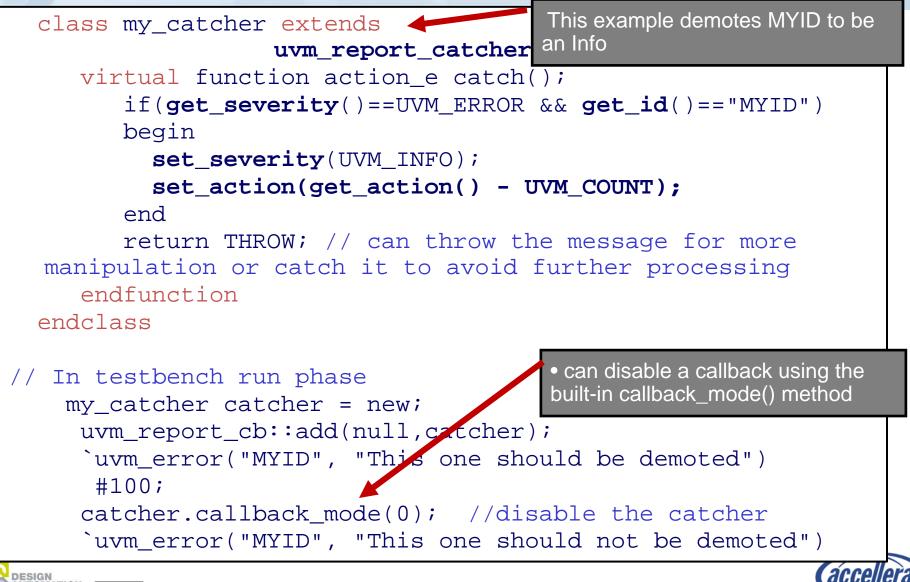

# **Extensions Using Callbacks**

- Like the factory, callbacks are a way to affect an existing component from outside

- The SystemVerilog language includes built-in callbacks

e.g. post\_randomize(), pre\_body()

- Callbacks requires the developer to predict the extension location and create a proper hook

- Callbacks advantages:

- They do not require inheritance

- Multiple callbacks can be combined

#### UVM Report Catcher Callback Goal: Message Manipulation

DAC Workshop on Universal Verification Methodology (UVM) - Verifying Blocks to IP to SOCs and Systems

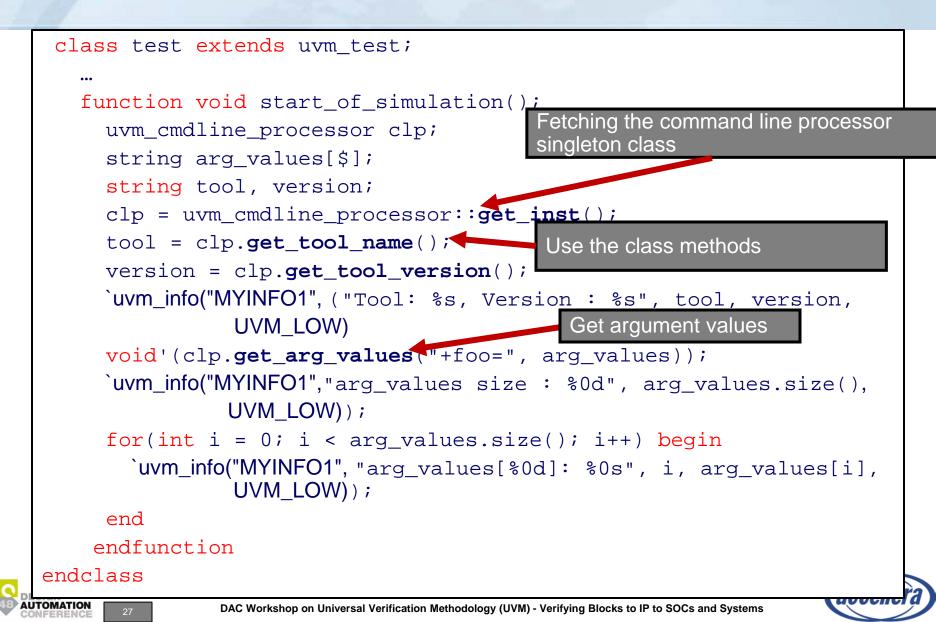

#### **Command-line Processor Class**

- Provide a vendor independent general interface to the command line arguments

- Supported categories:

- Basic Arguments and values

- get\_args, get\_args\_matches

- Tool information

- get\_tool\_name(), get\_tool\_version()

- Built-in UVM aware Command Line arguments

- Supports setting various UVM variables from the command line such as verbosity and configuration settings for integral types and strings

- +uvm\_set\_config\_int, +uvm\_set\_config\_string

#### **Command-line Processor Example**

# **UVM Concepts Summary**

- UVM Basics are proven and widely in use with all simulators

- Provides both reuse and productivity

- UVM1.0 adds additional features to complement and tune the existing capabilities

- UVM 1.1 includes bug fixes after initial users' feedback

- If you have a new project, UVM is the way to go!

# **Workshop Outline**

| ✓10:00am – 10:05am | Dennis Brophy    | Welcome                          |

|--------------------|------------------|----------------------------------|

| ✓10:05am – 10:45am | Sharon Rosenberg | UVM Concepts and Architecture    |

| 10:45am – 11:25am  | Tom Fitzpatrick  | UVM Sequences and Phasing        |

| 11:25am – 11:40am  | Break            |                                  |

| 11:40am – 12:20pm  | Janick Bergeron  | UVM TLM2 and Register Package    |

| 12:20pm – 12:50pm  | Ambar Sarkar     | Putting Together UVM Testbenches |

| 12:50pm – 1:00pm   | All              | Q & A                            |

#### **UVM Sequences & Phasing**

Tom Fitzpatrick Mentor Graphics

## Sequences

- Decouple stimulus specification from structural hierarchy

- Simple test writer API

- Sequences define transaction streams

- May start on any matching sequencer

- Sequences can call children

- Built-in get\_response() task

- Sequences & transactions customizable via the factory

- Driver converts transaction to pin wiggles

#### Using Sequences And Sequence Items

- A sequence is a UVM object to start it:

- Construction using the factory:

- spi\_tfer\_seq spi\_seq = spi\_tfr\_seq::type\_id::create("spi\_seq");

- Configure explicitly or via constrained randomization

- Start execution on the target sequencer:

- spi\_seq.start(spi\_sequencer);

- Within a sequence a sequence\_item is:

- Constructed

- Scheduled on a sequencer with start\_item()

- Blocking call that returns when the driver is ready

- Configured explicitly or via constrained randomization

- Consumed with finish\_item()

### Sequence\_Item Example

class spi\_seq\_item extends uvm\_sequence\_item;

// UVM Factory Registration Macro

`uvm\_object\_utils(spi\_seq\_item)

Data fields:

Request direction rand (stimulus generation)

Response direction non-rand

// Data Members (Outputs rand, inputs non-rand)

rand logic[127:0] spi\_data;

rand bit[6:0] no\_bits;

rand bit RX\_NEG;

```

// Analysis members:

logic[127:0] mosi;

logic[7:0] cs;

```

•UVM Object Methods

•These methods get generated by the automation macros

•Write them yourself to improve performance if desired

// Methods

extern function new(string name = "spi\_seq\_item");

extern function void do\_copy(uvm\_object rhs);

extern function bit do\_compare(uvm\_object rhs, uvm\_comparer comparer);

extern function string convert2string();

extern function void do\_print(uvm\_printer printer);

extern function void do\_record(uvm\_recorder recorder);

endclass:spi\_seq\_item

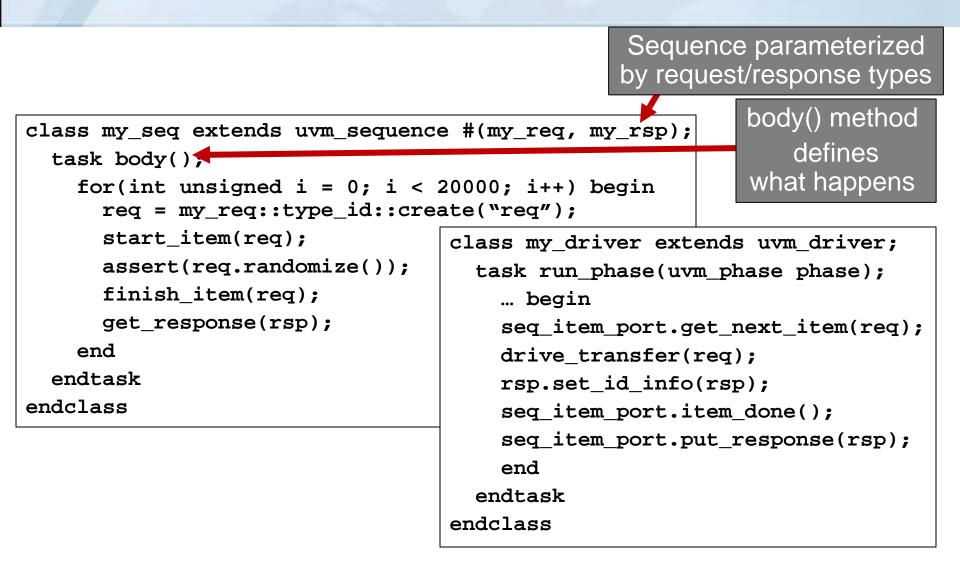

### **Basic Sequence-Driver API**

# **Sequence API Options**

```

Explicit

```

```

req = my_req::type_id::create("req");

start_item(req);

assert(req.randomize());

finish_item(req);

get_response(rsp);

```

#### **Using Macros**

`uvm\_do(req)

get\_response(rsp);

- Macros allow constraints to be passed in

- Macros require pre-defined callbacks to modify behavior

- Multiple macro variations

- Explicit API provides greater control and easier debug

### **Sequencer and Driver**

```

typedef uvm sequencer#(my req,my rsp) my sequencer;

class my master agent extends uvm agent;

function void build phase(uvm phase phase);

void'(uvm_config_db#(bitstream_t)::get(this,"", "is active", is a);

if(is a) begin

seqr = my sequencer::type id::create("seqr", this);

driver = my driver::type id::create("driver", this);

end

endfunction

function void connect phase(uvm phase phase);

if(is a)

driver.seq item port.connect(seqr.seq item export);

endfunction

agent

endclass

driver

segr

By default, you don't need

to extend uvm_sequencer

```

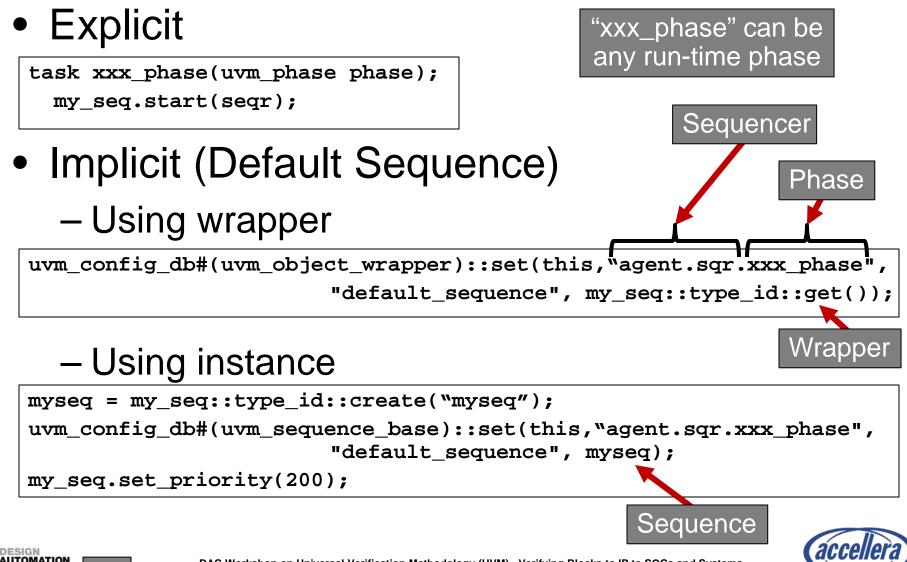

## **Starting a Sequence**

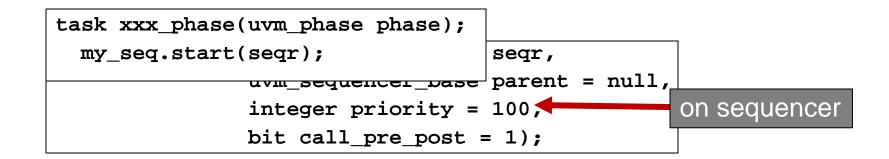

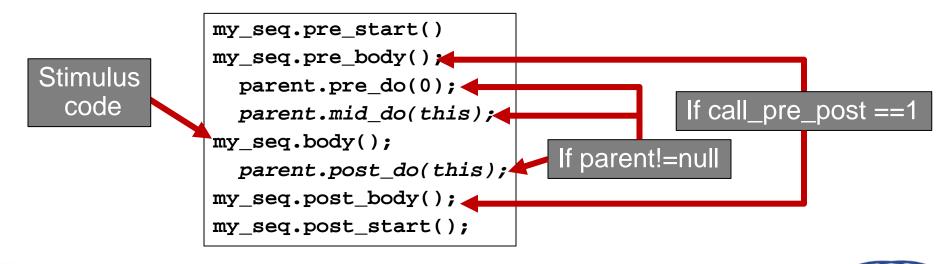

## **Calling start()**

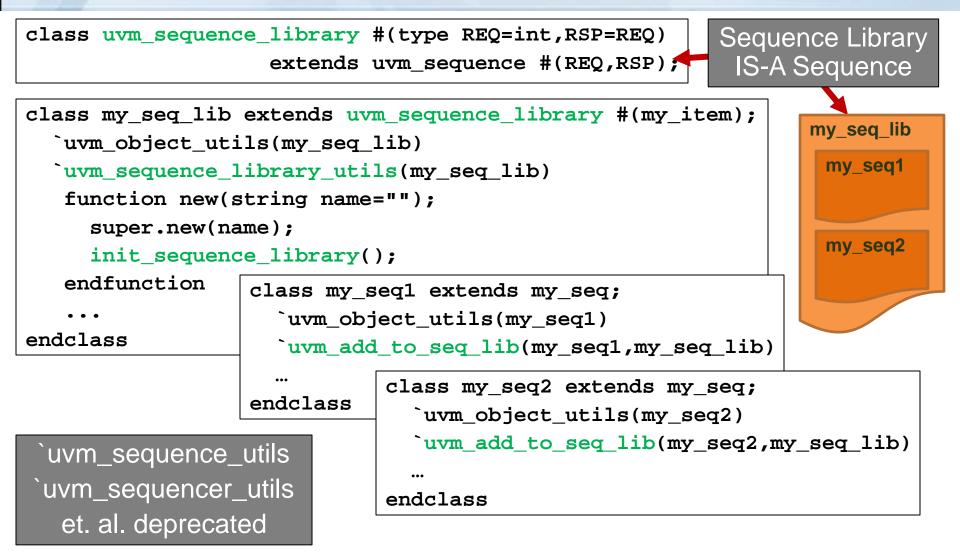

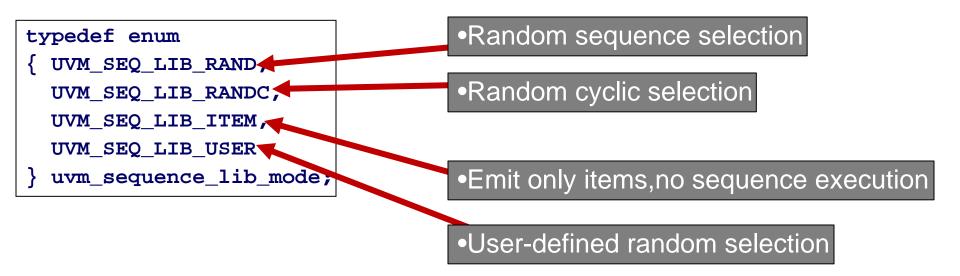

## Sequence Library (Beta)

## **Sequence Library**

uvm\_config\_db #(uvm\_sequence\_lib\_mode)::set(this, "sequencer.xxx phase", "default sequence.selection mode", MODE);

function int unsigned select\_sequence(int unsigned max);

// pick from 0 <= select\_sequence < max;

endfunction</pre>

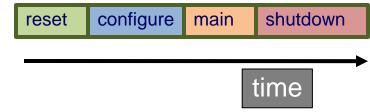

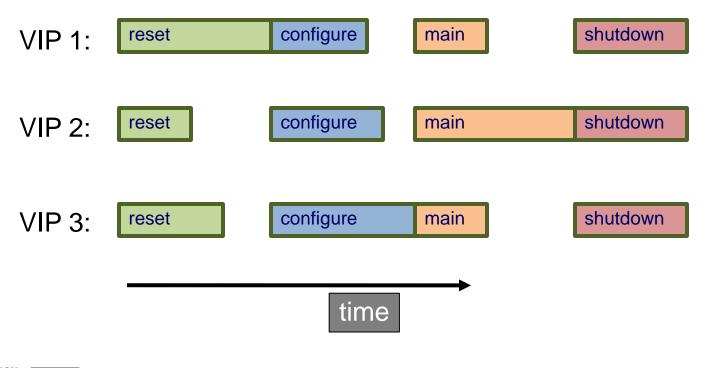

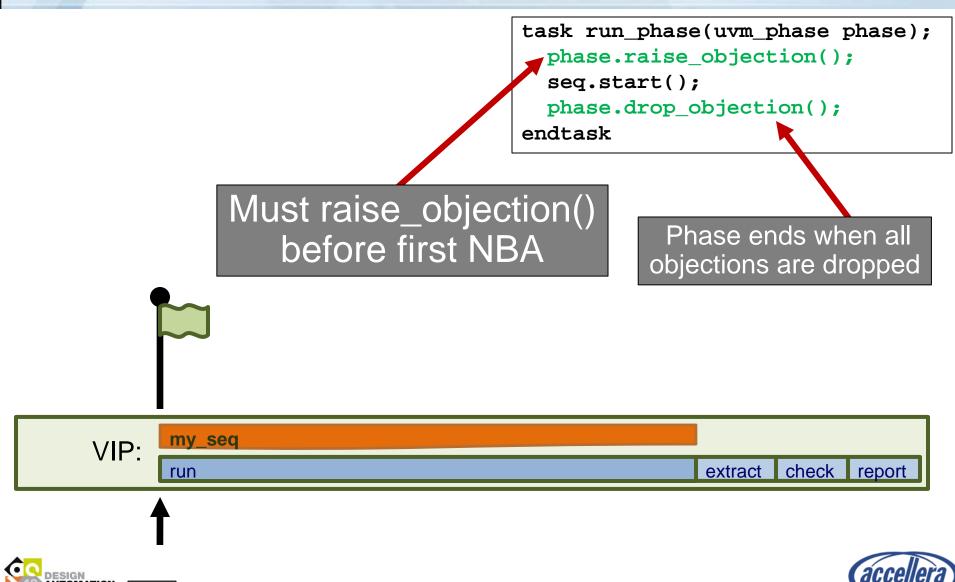

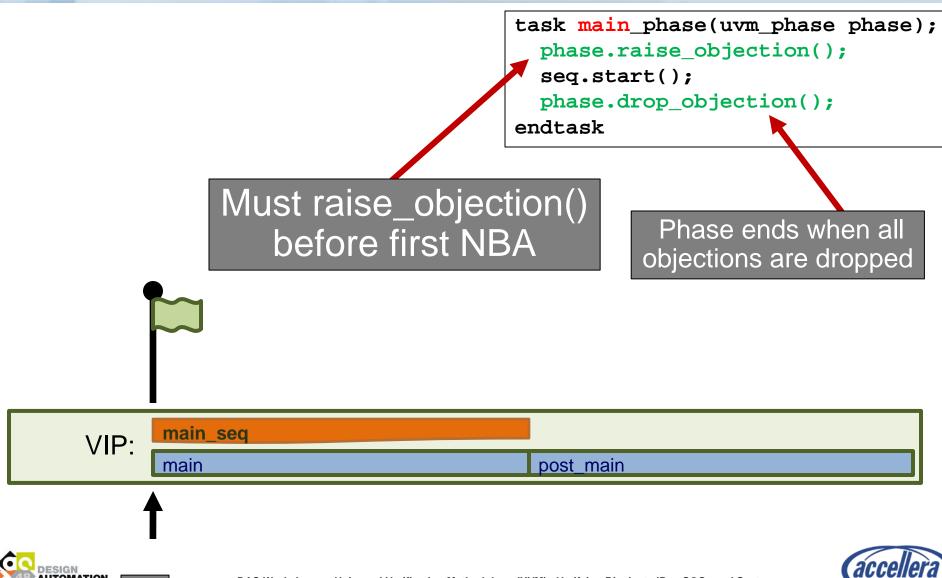

## **UVM** Phasing

Several new runtime phases / in parallel with run\_phase()

#### To simplify examples, these slides will show a reduced set of phases

## **Phase Synchronization**

By default, all components must allow all other components to complete a phase before all components move to next phase

42

## **Phase Semantics**

• In UVM Reference Guide, the semantics for each phase are defined, e.g.

reset

**Upon Entry**

•Indicates that the hardware reset signal is ready to be asserted.

- **Typical Uses**

- •Assert reset signals.

•Components connected to virtual interfaces should drive their output to their specified reset or idle value.

- •Components and environments should initialize their state variables.

- •Clock generators start generating active edges.

- •De-assert the reset signal(s) just before exit.

- •Wait for the reset signal(s) to be de-asserted.

#### **Exit Criteria**

- •Reset signal has just been de-asserted.

- •Main or base clock is working and stable.

- •At least one active clock edge has occurred.

- •Output signals and state variables have been initialized.

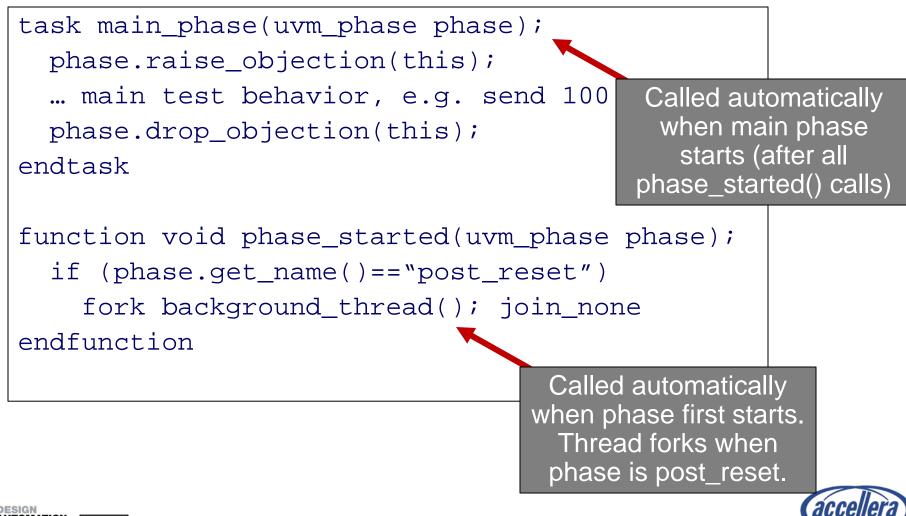

#### uvm\_component Basic API

Implement these to specify behavior for a specific phase; threads started here are auto-killed

task/function <name>\_phase(uvm\_phase phase)

phase.raise\_objection(this);

phase.drop\_objection(this);

Call these to prevent and re-allow the current phase ending

accelle

function void phase\_started(uvm\_phase phase)

function void phase\_ended(uvm\_phase phase)

Implement these to specify behavior for the start/end of each phase; threads started here are not auto-killed

DAC Workshop on Universal Verification Methodology (UVM) - Verifying Blocks to IP to SOCs and Systems

#### uvm\_component Example

45

## **User-defined Phases**

- Integrator can create one or more phases

- Integrator can create schedules with any mix of standard and user-defined phases then assign components to use one of those schedules

"want new phase named cfg2 after configure and before post\_configure"

New sched:

```

uvm_domain common =

uvm_domain::get_common_domain();

common.add(cfg2_phase::get(),

.after_phase(configure_phase::get(),

.before_phase(post_configure_phase.get())

);

```

configure cfg2 post\_configure

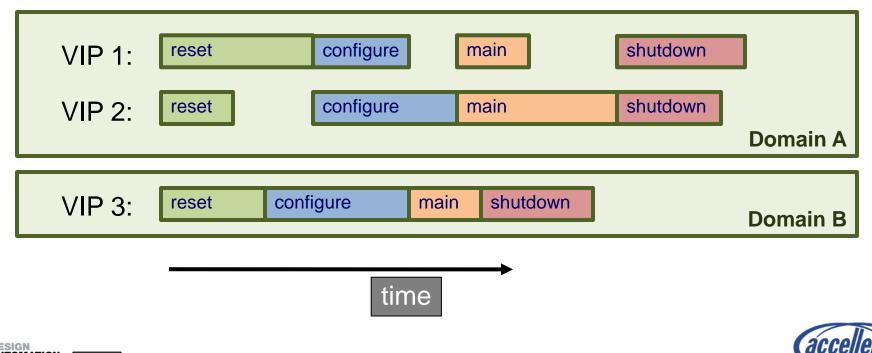

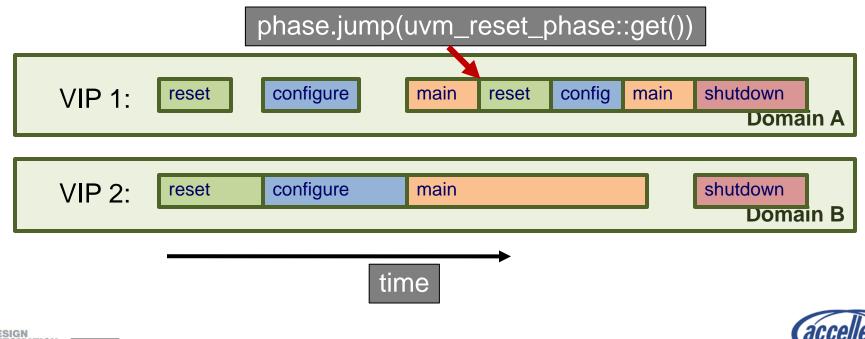

## **Separate Domains**

- Sometimes it is OK for a part of the design/environment to do behavior that is out of alignment with the remainder

- -e.g. mid-sim reset of a portion of the chip

- e.g. one side starts main functionality while other side is finishing configuration

#### Domains

48

- Domains are collections of components that must advance phases in unison

- By default, no inter-domain synchronization

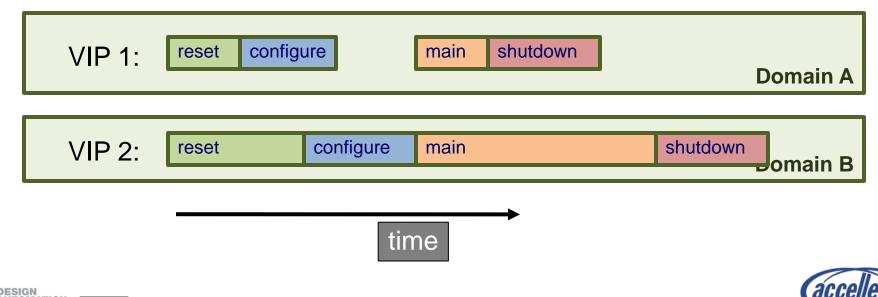

## **Domain Synchronization**

• Domains can be synchronized at one, many, or all phase transitions.

domainA.sync(.target(domainB),.phase(uvm\_main\_phase::get()));

Two domains sync'd at main

49

# **Fully Synchronized Domains**

If two domains are fully synchronized and one domain jumps back, the second domain will continue in its current phase and wait for the first to catch up

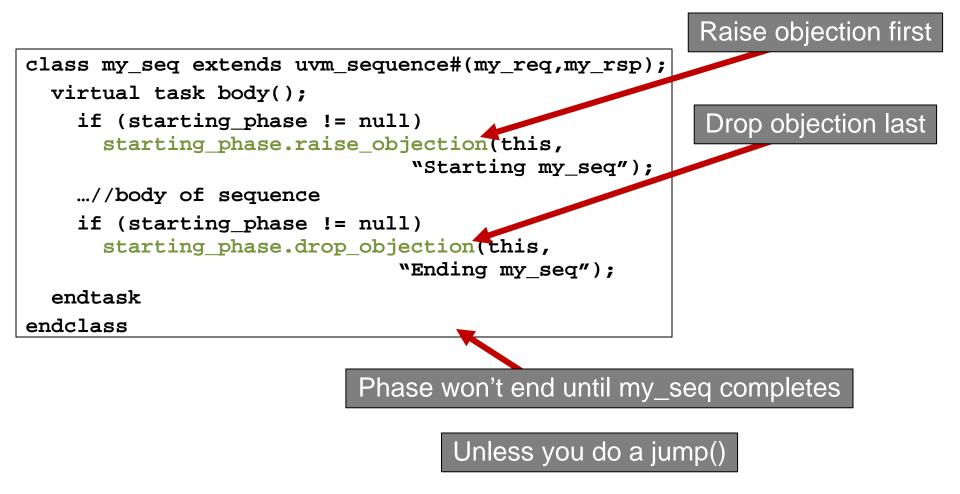

### **Sequences and Phases**

### **Ending Phases**

### **Ending Phases**

## **Delaying Phase End**

## **Ending Phases**

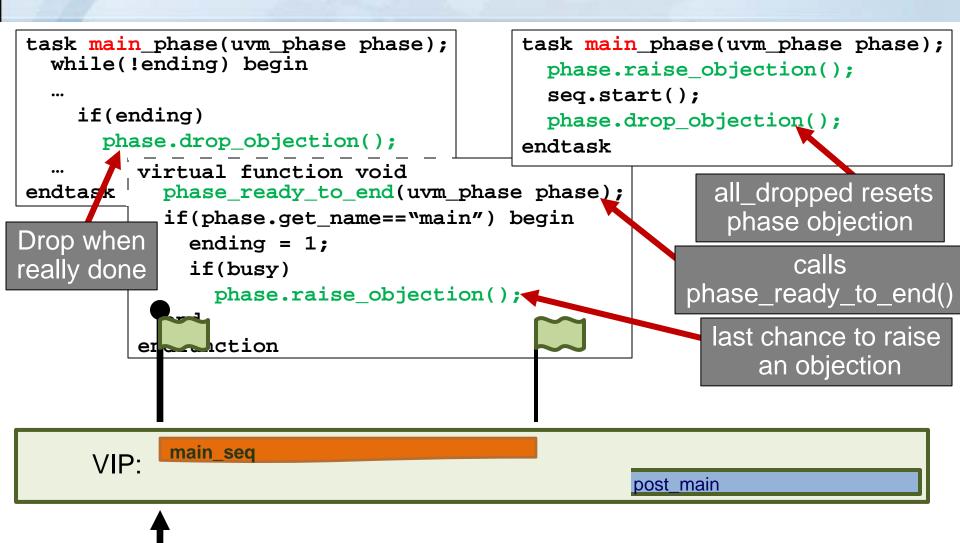

- Phase objection must be raised before first NBA

- Phase forks off processes

- wait for phase.all\_dropped

- call phase\_ready\_to\_end()

- component can raise objection

- Check objection count

- call phase\_ended()-

- kill\_processes

- execute successors

### **Test Phase Example**

```

task reset_phase (uvm_phase phase);

reset_seq rst = reset_seq::type_id::create("rst");

phase.raise_objection(this, "resetting");

(Test) Component runs different

sequences in each phase.

rst.start(protocol_sqr);

Phase level sequences may run

phase.drop_objection(this, "ending reset");

endtask: reset_phase

on different sequences in

parallel

task configure_phase (uvm_phase phase);

configure_seg cfg = configure_seg::type_id::create("cfg");

phase.raise_objection(this, "configuring dut");

cfq.start(protocol sqr);

phase.drop_objection(this, "dut configured");

endtask: configure_phase

task main_phase (uvm_phase phase);

test function1 seg tst = test function1 seg ::type id::create("tst");

phase.raise_objection(this, "functionality test");

tst.start(protocol_sqr);

phase.drop_objection(this, "functionality tested");

endtask: main_phase

```

# **Workshop Outline**

| ✓10:00am – 10:05am | Dennis Brophy    | Welcome                          |

|--------------------|------------------|----------------------------------|

| ✓10:05am – 10:45am | Sharon Rosenberg | UVM Concepts and Architecture    |

| ✓10:45am – 11:25am | Tom Fitzpatrick  | UVM Sequences and Phasing        |

| 11:25am – 11:40am  | Break            |                                  |

| 11:40am – 12:20pm  | Janick Bergeron  | UVM TLM2 and Register Package    |

| 12:20pm – 12:50pm  | Ambar Sarkar     | Putting Together UVM Testbenches |

| 12:50pm – 1:00pm   | All              | Q & A                            |

### **Accellera at DAC**

- Accellera Breakfast at DAC: UVM User Experiences

- An Accellera event sponsored by Cadence, Mentor, and Synopsys

- Tuesday, June 7<sup>th</sup>, 7:00am-8:30am, Room 25AB

#### Accellera IP-XACT Seminar

- An introduction to IP-XACT, IEEE 1685, Ecosystem and Examples

- Tuesday, June 7<sup>th</sup>, 2:00pm-4:00pm, Room 26AB

#### Birds-Of-A-Feather Meeting

- Soft IP Tagging Standardization Kickoff

- Tuesday, June 7, 7:00 PM-8:30 PM, Room 31AB

## **Workshop Outline**

| ✓10:00am – 10:05am | Dennis Brophy    | Welcome                          |

|--------------------|------------------|----------------------------------|

| ✓10:05am – 10:45am | Sharon Rosenberg | UVM Concepts and Architecture    |

| √10:45am – 11:25am | Tom Fitzpatrick  | UVM Sequences and Phasing        |

| √11:25am – 11:40am | Break            |                                  |

| 11:40am – 12:20pm  | Janick Bergeron  | UVM TLM2 and Register Package    |

| 12:20pm – 12:50pm  | Ambar Sarkar     | Putting Together UVM Testbenches |

| 12:50pm – 1:00pm   | All              | Q & A                            |

#### **UVM Transaction Level Modeling (TLM2)**

Janick Bergeron Synopsys

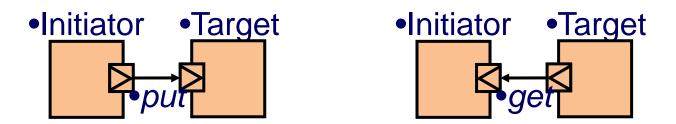

### **TLM-1.0**

Unidirectional put/get interfaces

- Simple message-passing semantics

- No response model

- E.g. What did I read back??

- Never really caught on in SystemC

## Why TLM-2.0?

- Better interoperability over TLM-1.0

- Semantics

- Pre-defined transaction for buses

- Performance

- Pass by reference (in SystemC)

- Temporal decoupling

## TLM-2.0 in SV vs SC

- Direct memory interface x

- Debug transport interface x

- Initiator sockets

- Target sockets

- Generic payload

- Phases

- Convenience sockets ×

- Payload event queue x

- Quantum keeper x

- Instance-specific extensions x

- Non-ignorable and mandatory extensions

- Temporal decoupling

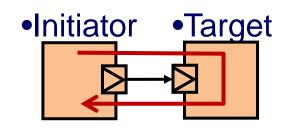

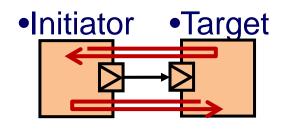

## **TLM-2.0 Semantics**

- Blocking

- When the call returns, the transaction is done

- Response is annotated

- Nonblocking

- Call back and forth

- Protocol state changes

- Transaction is updated

- Until one says "done"

## **Generic Payload Attributes**

Pre-defined bus transaction

| Attribute           | Туре                      | Modifiable?        |

|---------------------|---------------------------|--------------------|

| Command             | uvm_tlm_command_e         | No                 |

| Address             | bit [63:0]                | Interconnect only  |

| Data                | byte unsigned []          | Yes (read command) |

| Data length         | int unsigned              | No                 |

| Byte enable pointer | byte unsigned []          | No                 |

| Byte enable length  | int unsigned              | No                 |

| Streaming width     | int unsigned              | No                 |

| Response status     | uvm_tlm_response_status_e | Target only        |

| Extensions          | uvm_tlm_extension_base [] | Yes                |

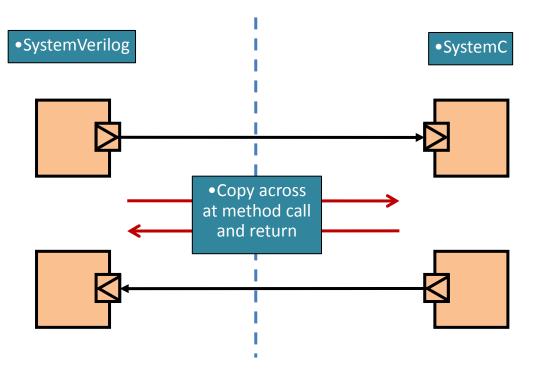

# **Connecting to SystemC**

- Tool-specific mechanism

- Not part of UVM

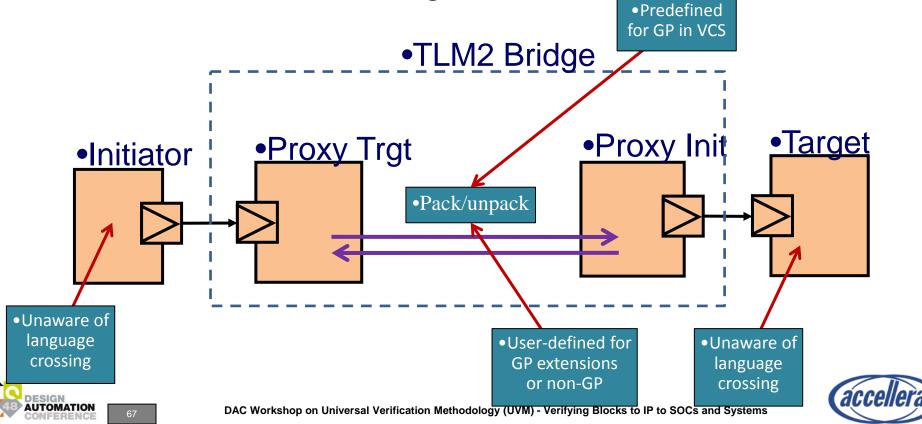

#### TLM-2.0 Bridge Between SV & SC

- Proxy sockets terminate the TLM2 connections in each language

- Create SV/SC bridge

# **UVM Register Model**

Janick Bergeron Synopsys

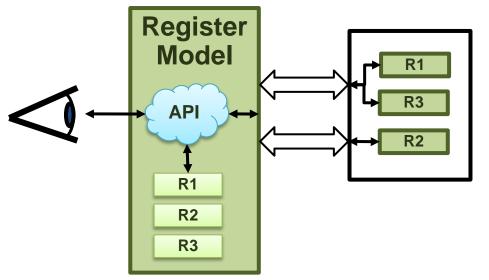

### **Overall Architecture**

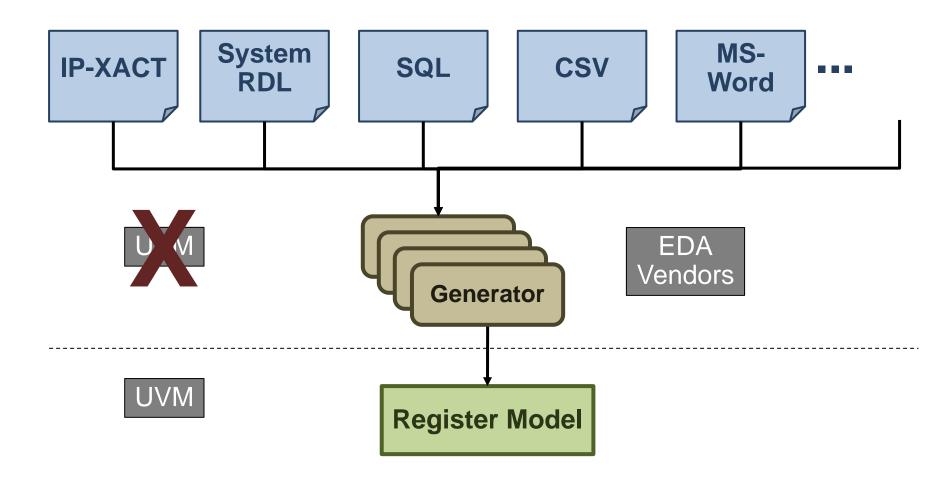

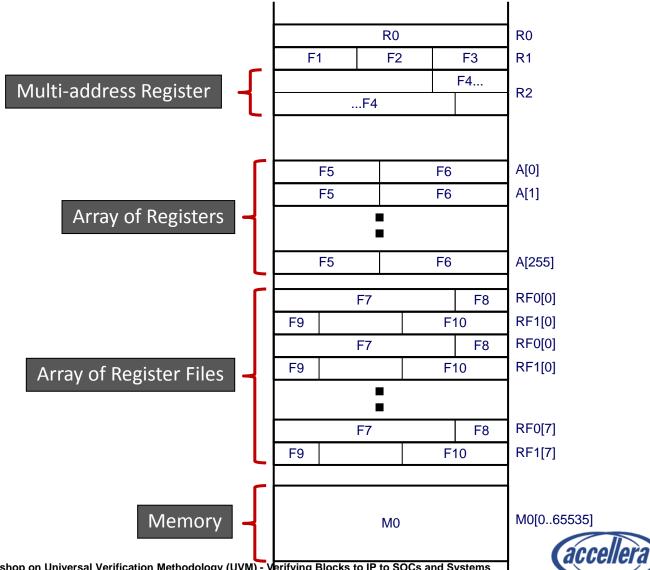

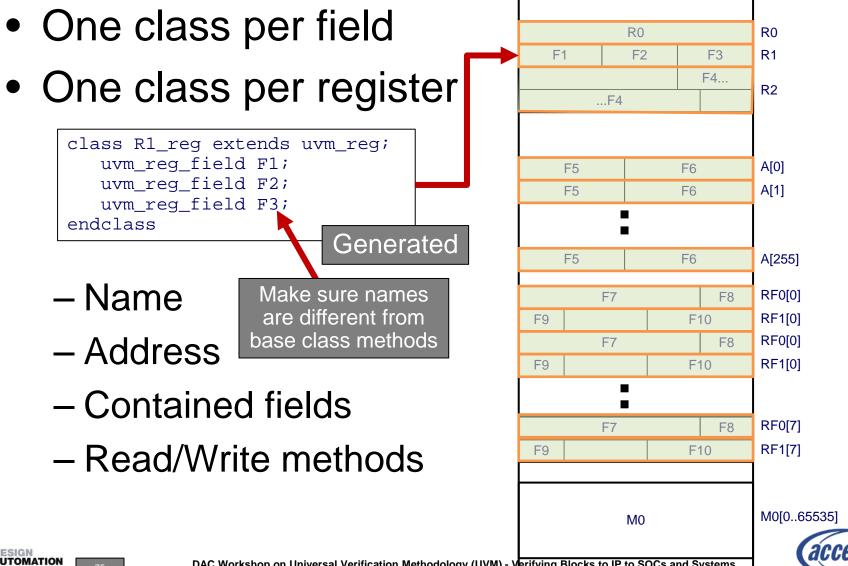

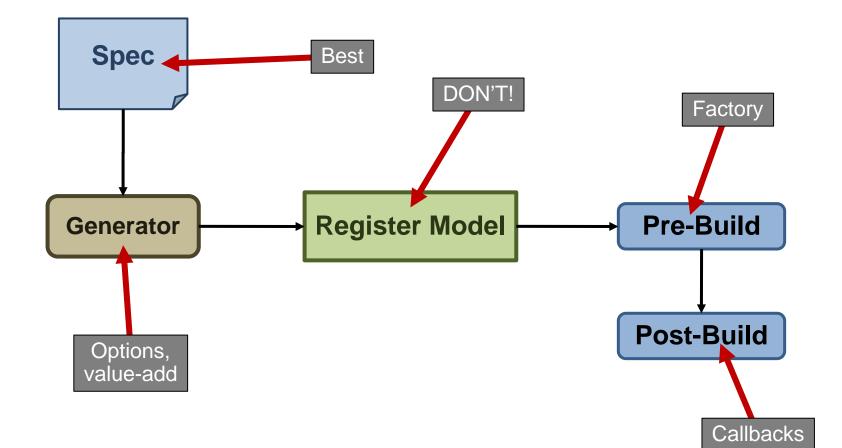

## **Specification & Generation**

accellera

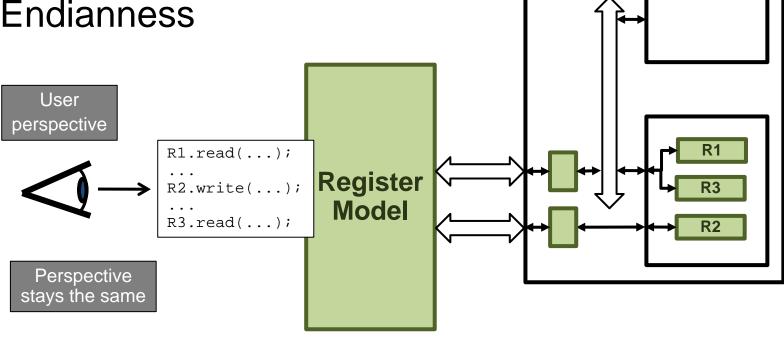

# **Physical Interfaces**

- Register model abstracts

- Physical interfaces

- Addresses

DUT may change

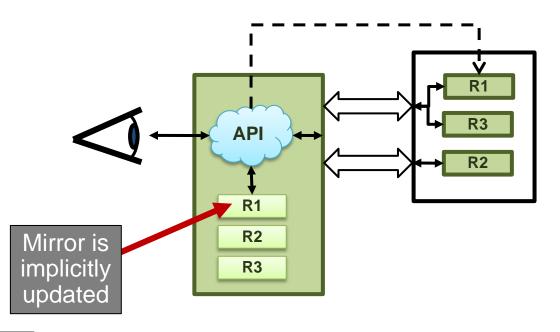

#### Mirror

- Register model mirrors content of registers in DUT

- "Scoreboard" for registers

- Updated on read and write()

- Optionally checked on read()

#### **Back-door Access**

- Must define HDL path to register in DUT – Generator-specific

- Access RTL directly in zero-time via VPI

- May affect simulator performance

#### **Programmer's View**

DAC Workshop on Universal Verification Methodology (UVM) - Verifying Blocks to IP to SOCs and Systems

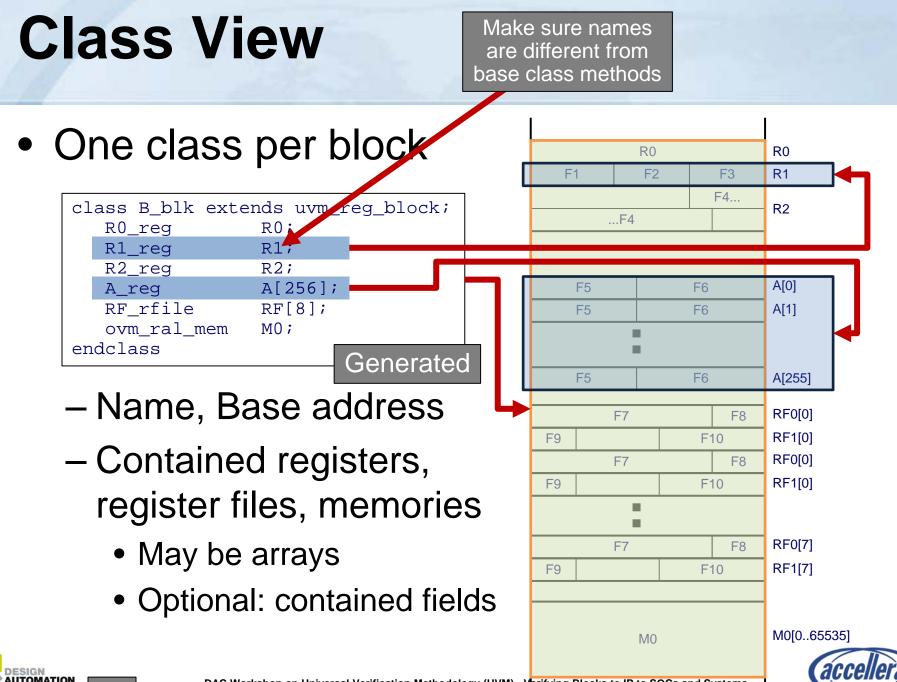

### **Class View**

DAC Workshop on Universal Verification Methodology (UVM) - Verifying Blocks to IP to SOCs and Systems

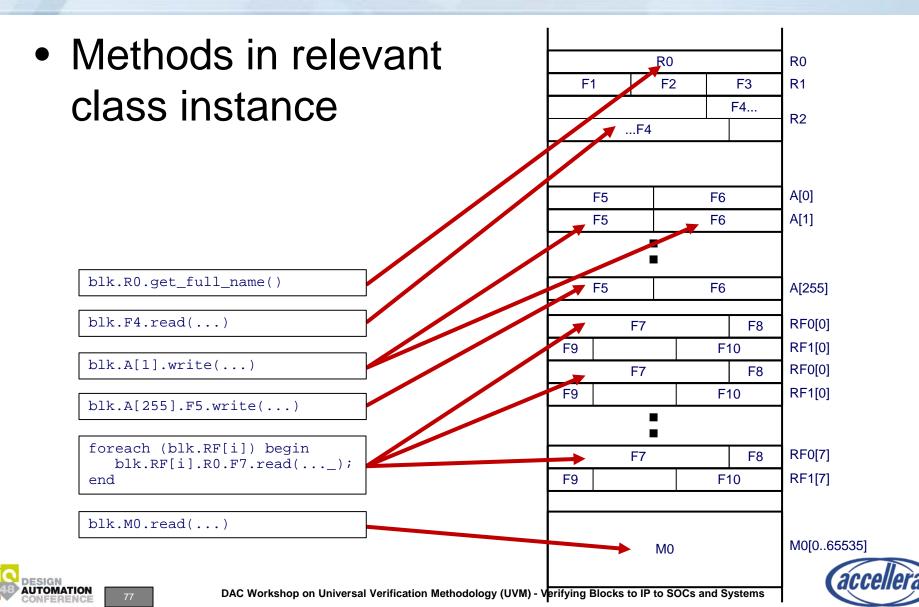

#### **API View**

## **Reading and Writing**

- Specify target register by hierarchical reference in register model

- Compile-time checking

blk.blk[2].regfile[4].reg.fld

By-name API also available

- Use read() and write() method on

- Register

- Field

- Memory

blk.blk[2].regfile[4].reg.fld.read(...);

blk.mem.write(...);

### **Register Sequences**

- Sequences accessing registers should be virtual sequences

- Not associated with a particular sequencer type

- Contain a reference to register model

- Access registers in body() task

```

class my_test_seq

extends uvm_sequence;

```

```

my_dut_model regmodel;

```

```

virtual task body();

regmodel.R1.write(...);

regmodel.R2.read(...);

...

endtask

endclass

```

#### **Register Sequences**

- Includes pre-defined sequences

- Check reset values

- Toggle & check every bit

- Front-door/back-door accesses

- Memory walking

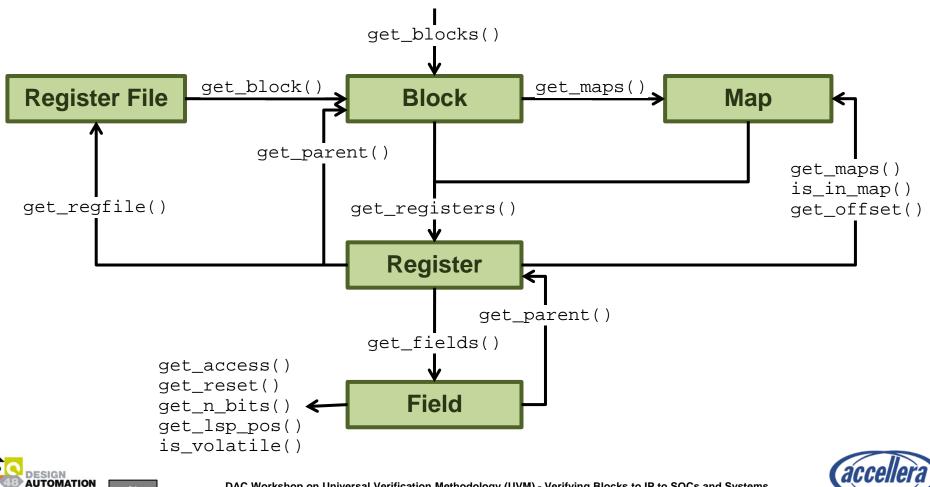

#### Introspection

Rich introspection API

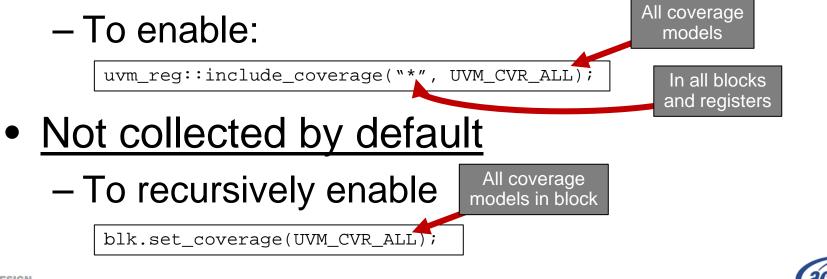

## **Coverage Models**

- Register models *may* contain coverage models

- Up to the generator

- Not instantiated by default

- Can be large. Instantiate only when needed.

#### **Customization Opportunities**

## There's a <u>LOT</u> more!

- DUT integration

- Multiple interfaces

- Randomization

- Vertical Reuse

- "Offline" access

- User-defined front-door accesses

- Access serialization

- Pipelined accesses

### **Workshop Outline**

|  | ✓10:00am – 10:05am | Dennis Brophy    | Welcome                          |

|--|--------------------|------------------|----------------------------------|

|  | ✓10:05am – 10:45am | Sharon Rosenberg | UVM Concepts and Architecture    |

|  | ✓10:45am – 11:25am | Tom Fitzpatrick  | UVM Sequences and Phasing        |

|  | √11:25am – 11:40am | Break            |                                  |

|  | ✓11:40am – 12:20pm | Janick Bergeron  | UVM TLM2 and Register Package    |

|  | 12:20pm – 12:50pm  | Ambar Sarkar     | Putting Together UVM Testbenches |

|  | 12:50pm – 1:00pm   | All              | Q & A                            |

#### **Putting Together UVM Testbenches**

#### Ambar Sarkar Paradigm Works, Inc.

#### Agenda

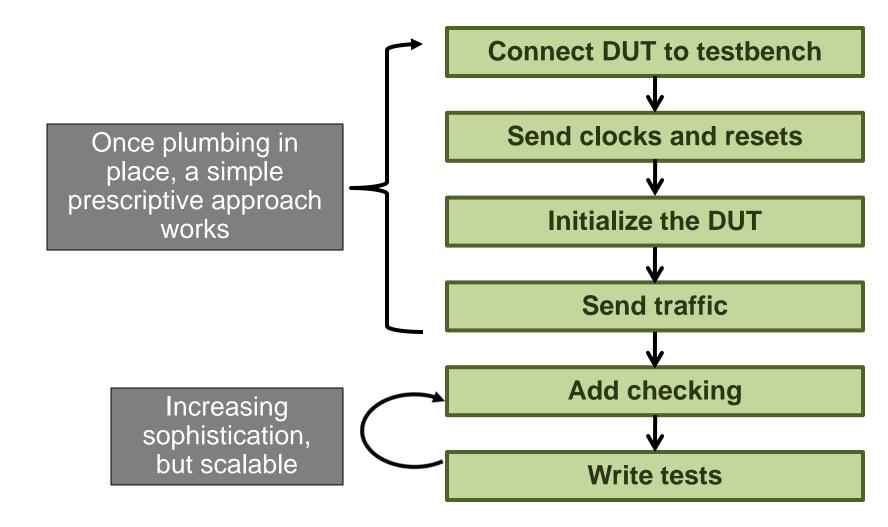

- Case studies

- Several UVM1.0 environments deployed

- Currently in production

- Novice to sophisticated teams

- Getting started with UVM is relatively easy

- Basic tasks remain simple

- Were able to use a "prescriptive" approach

- Iteratively developed and scales to any complexity

- Advanced uses

- Unit to system-level

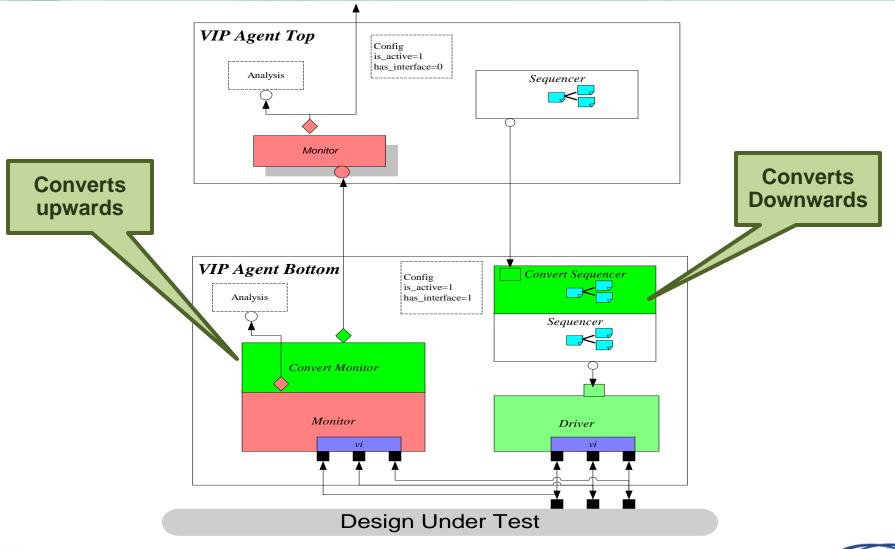

- VIP Stacking/Layering

### **Implementing Basic Steps**

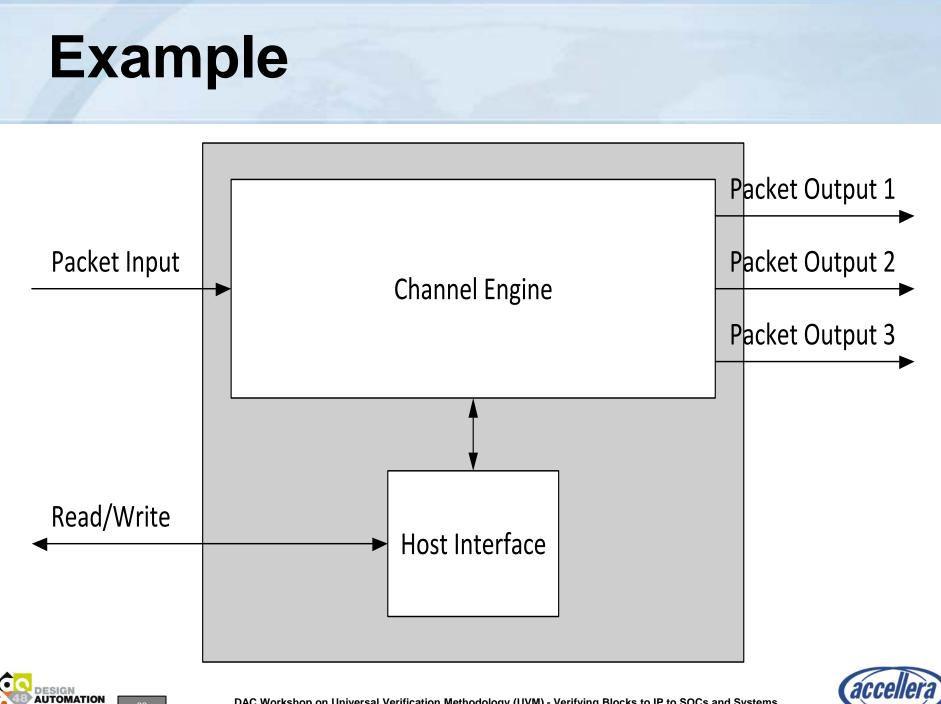

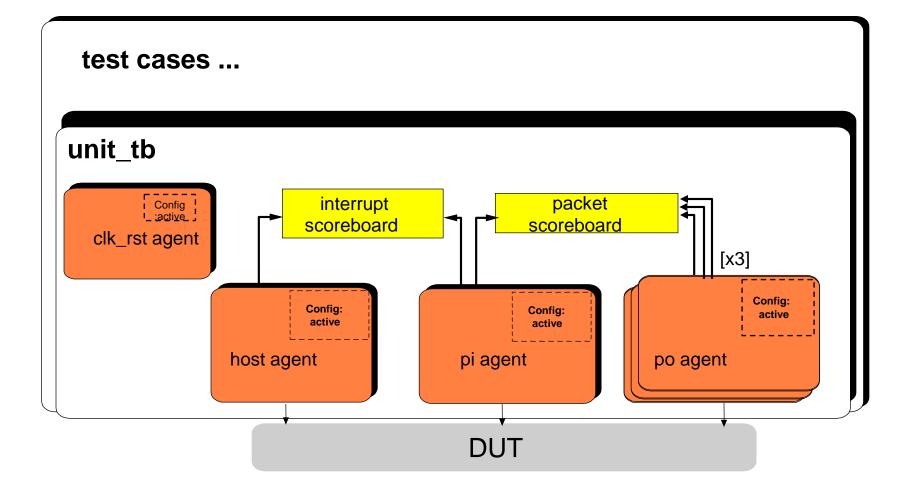

#### **Example Environment in UVM**

#### **Connect DUT to Testbench**

Always use SystemVerilog interface

Use clocking blocks for testbench per interface

Use modports for DUT

e Packet Output 1 Packet Output 2 Packet Output 3 Packet Output 3

#### **Connect Clock and Resets**

```

Combine clock and reset as agents in one env

```

```

class clk_rst_env extends uvm_env;

clk_rst_cfg cfg; //! VIP configuration object

//! bring ports out for convenience

uvm_analysis_port #(uvm_transaction) rst_mon_ap_out;

//! Agents in env

clk_agent clk_agt;

rst_agent rst_agt;

...

```

#### Define reset as sequences

## Initializing the DUT

Add transaction definitions for configuration interface (host) Add driver code for host

Setup host initialization seq

```

class host transaction extends uvm_sequence_item;

rand bit[31:0] hi addr;

rand bit[7:0] hi wr data;

task pwr hi master driver::drive transaction(host transaction trans);

if (trans.trans kind == PWR HI WR) begin

intf.hif address = trans.hi addr;

intf.hif data = trans.hi wr data;

task my env init sequence::body();

regmodel.R1.write(...);

regmodel.R2.read(...);

```

### **Sending traffic**

#### Similar to initialization

#### Sequences differ

```

//! sequence body.

task pi sequence::body();

pi transaction#(. . .) req_xn;

cfg inst = p sequencer.cfg;

forever begin

p sequencer.peek port.peek(req xn);

if (!this.randomize()) begin

`uvm_fatal({get_name(), "RNDFLT"}, "Can't randomize");

end

`uvm do with(this transaction,

trans kind == req xn.trans kind;

read_vld_delay inside { [0:15] };

});

```

## **Checking and Writing Tests**

Add checking in the environment Add monitor code for all components Connect the scoreboards

```

class my env extends uvm env;

unit_scoreboard#(uvm transaction, uvm transaction) sb;

function void my env::build phase(uvm phase phase);

sb = unit scoreboard#(uvm transaction, uvm transaction)

::type_id::create({get_name(), "_sb"}, this);

function void pwc env::connect phase(uvm phase phase);

pi mon.mon ap out.connect(sb.post export);

po mon.mon ap out.connect(sb.check export);

Add test-specific checking in the test as needed

```

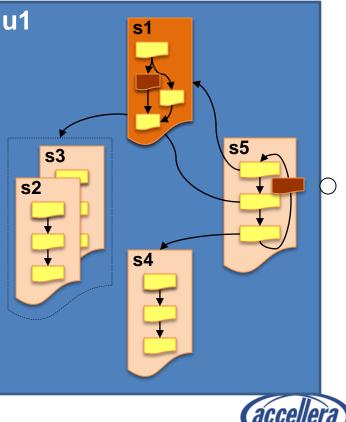

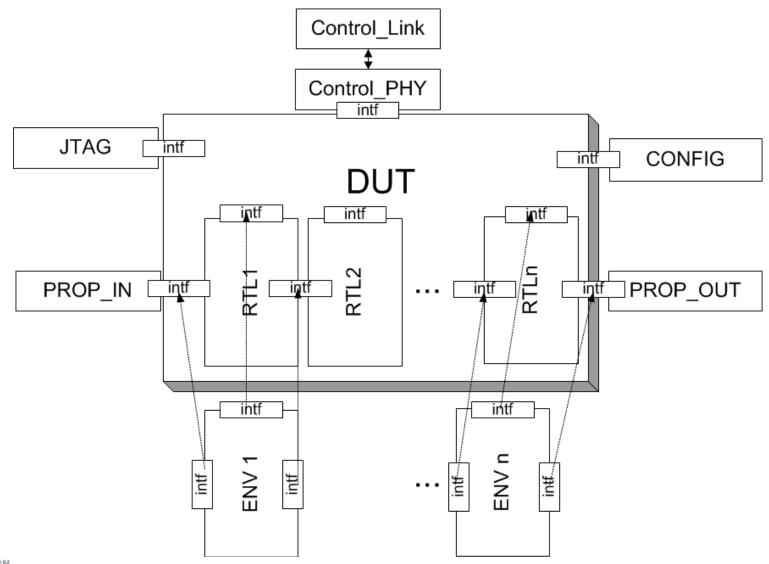

#### **Connecting Unit to System Level**

DAC Workshop on Universal Verification Methodology (UVM) - Verifying Blocks to IP to SOCs and Systems

accellera

#### **Connecting Unit to System Level: Reuse**

- Scoreboarding

- Reuse SB encapsulated within sub-envs

- Chain the scoreboards

- Functional Coverage

- Needed to filter coverage points

- Reuse monitors

- Avoid duplicated instances

- Gate Simulations

- Disable monitors

- Disable internal scoreboards

- Registers

- Register abstraction reused, but different interfaces used

- Configurations

- Defined separate system configuration

- Top level instantiated sub-env configurations

- Sequences

- Virtual sequencer only at the system level

- Initialization sequences reused from unit-level

- Traffic sequences created from scratch at the system level

#### **Connecting Unit to System Level: Prescription**

For each sub-env class

Extend sub-env base class

Make all internal components passive

Added sub-env config object to your system config

Declare at system-level:

unit\_env\_cfg unit\_env\_cfg\_inst;

`uvm\_field\_object(unit\_env\_cfg\_inst, UVM\_REFERENCE)

Turn off virtual sequencer at the unit level

## **VIP Stacking/Layering**

accellera

#### Summary

Getting started with UVM was relatively easy Once initial plumbing in place Basic tasks remain simple Were able to use a "prescriptive" approach Able to iteratively develop testbench Scales to any complexity Unit to system Stacking of VIPs Deployed across projects and simulation vendors Worked with minor gotchas No UVM issues found Some SystemVerilog support issues among vendors e.g. Inout ports and modports and clocking blocks

### **Workshop Outline**

| ✓10:00am – 10:05am | Dennis Brophy    | Welcome                          |

|--------------------|------------------|----------------------------------|

| ✓10:05am – 10:45am | Sharon Rosenberg | UVM Concepts and Architecture    |

| ✓10:45am – 11:25am | Tom Fitzpatrick  | UVM Sequences and Phasing        |

| √11:25am – 11:40am | Break            |                                  |

| ✓11:40am – 12:20pm | Janick Bergeron  | UVM TLM2 and Register Package    |

| ✓12:20pm – 12:50pm | Ambar Sarkar     | Putting Together UVM Testbenches |

| 12:50pm – 1:00pm   | All              | Q & A                            |

#### **Questions?**

- Download UVM from <u>www.accellera.org</u>

- Reference Guide

- User Guide

- Reference Implementation

- Discussion Forum

#### **Accellera at DAC**

#### • Accellera Breakfast at DAC: UVM User Experiences

- An Accellera event sponsored by Cadence, Mentor, and Synopsys

- Tuesday, June 7<sup>th</sup>, 7:00am-8:30am, Room 25AB

#### Accellera IP-XACT Seminar

- An introduction to IP-XACT, IEEE 1685, Ecosystem and Examples

- Tuesday, June 7<sup>th</sup>, 2:00pm-4:00pm, Room 26AB

#### Birds-Of-A-Feather Meeting

- Soft IP Tagging Standardization Kickoff

- Tuesday, June 7, 7:00 PM-8:30 PM, Room 31AB

# Lunch in Room 20D Show your Workshop Badge for entry

DAC Workshop on Universal Verification Methodology (UVM) - Verifying Blocks to IP to SOCs and Systems

DAC Workshop on Universal Verification Methodology (UVM) - Verifying Blocks to IP to SOCs and Systems